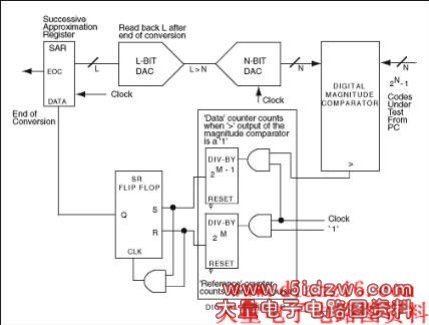

Figure 5. Successive approximation and a DAC configuration replace the integrator section of the analog servo loop.

The advantage of an averaging circuit is apparent when noise causes the magnitude comparator to toggle and become unstable, as it does on approaching its final result. Two divide-by counters are included in the averaging circuit. The "reference" counter has a period of 2M clock cycles, where M is a programmable integer governing the period (and hence the test time). A "data" counter, which increments only when the magnitude comparator output is high, has a period equal to one-half of the first 2M-1 cycles.

Together, the reference and data counters average the number of highs and lows, store the result in a flip-flop, and pass it on to the SAR register. This procedure is repeated 16 times (in this case) to generate the complete output code word. Like the previous method, this one has advantages and disadvantages:

- The test setup's input voltage is defined digitally, allowing easy modification of the number of samples over which the result is to be averaged.

- The SAR approach provides a DC level rather than a ramp at the DUT's analog input.

- As a disadvantage, the DAC in the feedback loop sets a finite limit on resolution of the input voltage.

SAR Converter

A SAR converter works like the old-fashioned chemist's balance. On one side is the unknown input sample, and on the other is the first weight generated by the SAR/DAC configuration (the most significant bit, which equals half of the full-scale output). If the unknown weight is larger than 1/2FSR, this first weight remains on the balance and is augmented by 1/4FSR. If the unknown weight is smaller, the weight is removed and replaced by a weight of 1/4FSR.

The SAR converter then determines the desired output code by repeating this procedure N times, progressing from the MSB to the LSB. N is the resolution of the DAC in the SAR configuration, and each weight represents 1 binary bit.

Dynamic Testing of INL and DNL

To assess an ADC's dynamic nonlinearity, you can apply a full-scale sinusoidal input and measure the converter's signal-to-noise ratio (SNR) over its entire full-power input bandwidth. The theoretical SNR for an ideal N-bit converter (subject only to quantization noise, with no distortion) is as follows:

SNR (in dB) = N×6.02 +1.76.

Embedded in this figure of merit are the effects of glitches, integral nonlinearity, and sampling-time uncertainty. You can obtain additional linearity information by performing the SNR measurement at a constant frequency and as a function of the signal amplitude. Sweeping the entire amplitude range, for example, from zero to full scale and vice versa, produces large deviations from the source signal, as source amplitude approaches the converter's full-scale limit. To determine the cause of these deviations, while ruling out the effects of distortion and clock instability, use a spectrum analyzer to analyze the quantization-error signal as a function of frequency.

Countless other approaches are available for testing the static and dynamic INL and DNL of both high- and low-speed data converters. The intent here has been to give you a better understanding of the generation of powerful TOCs (typical operating characteristics) using tools and techniques that are simple but still smart and precise.

References

- MAX108 data sheet, Rev. 1, 5/99, Maxim Integrated Products.

- MAX108EVKIT data sheet, Rev. 0, 6/99, Maxim Integrated Products.

- Analog Integrated Circuit Design, D. Johns & K. Martin, John Wiley & Sons Inc., 1997.

- Low-Voltage/Low-Power Integrated Circuits and Systems, Low-Voltage Mixed-Signal Circuits, E. Sanchez-Sinencio & A. G. Andreou, IEEE Press Marketing, 1999.

- Integrated Analog-to-Digital and Digital-to-Analog Converters, R. van de Plasche, Kluwer Academic Publishers, 1994.