在电源分配网络中元件的转换常会引起电流的波动,由于电压下降,电流的扰动会导致器件的功能异常。在最大容性负载情况下,大电容既可为电路提供能量储存,又可以给元件提供直流电压及电流,从而为电路提供稳定的最佳电压和电流,以实现对数据、编码及同步控制信号的转换。

一般,在每两个LSI和VLSI器件之间要放一个大电容,另外在下面几处位置也需放置去耦电容。

・ 电源与PCB的接口处。

・ 功率损耗电路和元器件的附近。

・ 自适应卡、外围设备和子电路I/O接口与电路终端连接处。

・ 输入电压连接器的最远位置。

・ 时钟发生电路和脉动敏感器件附近。

・ 远离直流电压输入连接器的高密元件布置。

在储存器阵列中,由于它的状态恢复需要额外的电流,因此,同样需要大电容。多引脚的VLSI、高密度PGA模块基于同样的道理,也需要连接额外的大电容,以保证最大容性负载情况下信号、编码和控制引脚同步地顺利切换。

在使用大电容时,一般以标称电压等于实际需要的额定电压的50%来计算额定电压,从而避免在冲激电压下电容的毁坏。举例而言,如果电压为5V,则应该用额定电压为10V的电容。

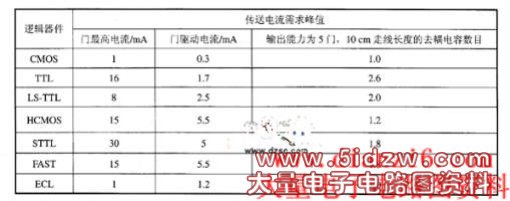

如表所示,给出了常见逻辑门器件所需要的去耦电容数目。此表是在最大允许下降电压时,能对电路去噪25%的情况下获得的。表中的数据对标准的CMOS器件而言是相当保守的,这是因为在没有太大压降时,器件的连接线无法提供所需的峰值电流。

表 逻辑器件需要的去耦电容数目

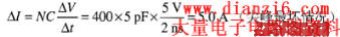

利用前面讲述的电容能量储存属性的电流计算公式,可计算被电容消耗的峰值电流。工程实践表明,电容并不是越大越好,过大的电容会消耗大量的电流,对高速电路的输入功率有很高的要求。

应该注意的是,根据以往在低速逻辑器件下获得的经过挑选的电容,并不适用于高速电路中的旁路和去耦。谐振、PCB的放置、引线的电感,以及其他因素都是在选择电容时需要考虑的。

通过下边的方法,可以获得理想的最佳大电容。

(1)假设板上的所有切换器件同时开关,获得了最大的损耗电流,其中包括逻辑交叉产生的电压冲激效应(交叉电流)。

(2)计算允许的最大电源噪声容限ΔV。

(3)判断电路允许的最大共路径阻抗Zcn:

(4)如果使用实心板,则应分配好连接电源和接地层的连接阻抗Zcn。

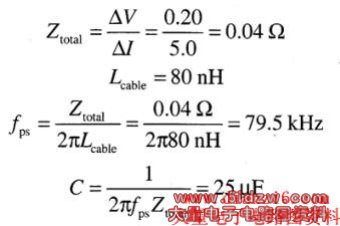

(5)计算从电源到板之间连接电缆的阻抗Zcable,在电源合理布线的基础上,通过Ztotal=Zcn+Zcable来决定频率。

(6)如果实际切换频率低于上式中的计算频率f,则电源布线是合理的。若高于f,则需要加电容Cbulk。在频率为f,阻抗为Ztotal时,可通过下式计算出所需的电容值。

例:假设一块安装有400个CMOS器件的PCB,在2ns时钟周期内产生5pF的切换负载,电压源的电感为80nH,计算所需去耦旁路电容的大小。

估计最大噪声容限值:ΔV=0.20v

PCB上常见的大电容值-般为10~100μF。

通过获得需要去耦的逻辑器件的谐振工作频率,可以得到器件的切换能量,从而能够计算出PCB所需要的射频电流的去耦电容。其中的难点在于必须知道器件引线的电感ESL才能计算谐振频率。实践中,可以利用阻抗分析仪或网络分析仪去测量ESL。但阻抗分析仪是低频仪器,无法测量高频响应。ESL还可以通过已知电容值和寄生振荡频率获得。

欢迎转载,信息来源www.5idzw.com(www.5idzw.com)

,大电容的选择举例