摘要: SoC是超大规模集成电路的发展趋势和新世纪集成电路的主流[1]。其复杂性以及快速完成设计、降低成本等要求,决定了系统级芯片的设计必须采用IP(Intellectual Property)复用的方法。本文介绍以可复用IP设计方法,设计串行外设接口SPI(Serial Peripheral Interface)模块IP核的思路,用Verilog语言实现,并经FPGA验证,通过TSMC(台湾集成电路制造公司)的0.25μm工艺生产线流水实现,完成预期功能。

关键词: SoC 可复用IP SPI AMBA总线

引 言

随着集成电路设计技术和深亚微米制造技术的飞速发展,集成电路的规模越来越大,出现了片上系统SoC(System on Chip,又称之为系统级芯片)。由于其在速度、功耗和成本方面的优势,发展势头迅猛。SoC芯片是一个复杂的系统,为了在规定时间完成设计,并提高设计的可靠性,只有依赖基于IP复用的SoC设计方法。如何为SoC设计提供可复用的IP核,成为SoC设计的基础和难点。

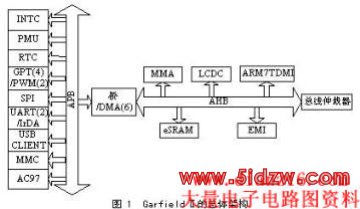

东南大学ASIC系统工程技术研究中心针对AMBA(Advanced Microcontroller Bus Architecutre,先进微控制器)总线规范开发了一款代号为Garfield的嵌入式微处理器。此微处理器除采用ARM公司ARM7TDMI内核的硬IP外,其余模块采用了自己开发的软IP。本文以串行外设接口SPI为例,介绍基于复用的IP设计与验证的一些经验。此SPI模块基于AMBA的APB(Advanced Peripheral Bus,先进外设总线)规范,可以不作修改地应用在任何符合AMBA总线规范的微处理器设计中。

Garfield的总体架构及SPI模块在系统中所处的位置如图1所示。

1 可复用IP核的SoC设计方法

系统级芯片设计中,IP特指经过验证的各种超级宏单元模块电路。VSIA(虚拟器件接口联盟)根据设计层次,将IP划分为三个层次:硬IP、软IP和介于两者之间的固IP。硬IP性能最优但适应性较差,软IP灵活性大、可移植性好。IP核必须具有以下特征[2]:①可读性;②设计的衍展性和工艺适应性;③可测性;④端口定义标准化;⑤版权保护。

代码编写规则和可综合的书写规范是实现IP核的基础,可保证IP软核在任何EDA工具下编译和综合的正确性。为SoC集成时消除综合产生的风险,我们制定了Verilog代码的书写规范,并要求有详细的注释,易于他人理解和修改。可复用IP设计流程如图2所示[3]。

为了容易地将IP集成到芯片中,需要标准化的接口或片上总线,VSIA在这方面作了一定的工作。另外,设计中要尽量将IP核接口部分与功能部分分开,单独作为一模块进行设计,当需要集成到其它互连协议中时,只需修改接口部分。为尽可能地提供灵活性,允许综合时设置多个参数。

在最终面向用户的产品发布中,用户手册是非常重要的部分。这部分文档将被用于IP核的选择、集成和验证,是一种非常专业化的文档。它主要包括模块系统结构、功能框图、输入/输出口、时序图、调用方式、设计流程、测试指导、推荐使用的软件编译器和驱动程序、系统验证指导、调试指导和该IP核版本历史等。在可重用IP核产品发布中,还应包含该IP核的多种仿真模型,以便用户在进行评估、设计和系统测试时使用。IP核的仿真模型一般可分为3个层次:①行为级模型,能够仿真该IP核的全部功能,包括在算法级和指令集上的功能;②硬件级模型,能够精确提供该IP核的功能和时序的仿真;③门级模型,提供硬核的带有时序反标注信息的仿真模型。

在实践中,我们摸索出一套基于CVS(协作版本管理系统)的版本管理和设计、验证人员协同工作的制度流程,对RTL代码作了尽可能全面的仿真,提供完备的测试矢量,保证了最终IP核的质量,并按要求建立了标准、规范的文档。

2 SPI模块IP核的设计

串行外围设备接口SPI(Serial Peripheral Interface)总线技术是Motorola公司推出的多种微处理器、微控制器以及外设间的一种全双工、同步、串行数据接口标准[4]。SPI总线是一种三线总线,因其硬件功能很强,所以,与SPI有关的软件就相当简单,使CPU有更多的时间处理其它事务。

2.1 SPI模块的接口信号及时序要求

(1)内部总线接口

AMBA规范是由ARM公司制定的片上总线规范,为SoC的设计提供了以下优点:较好的可移植和可复用设计、低功耗设计、高性能和结构可移植的系统设计以及较好的可测性设计[5]。SPI是APB总线上的Slave模块。APB总线时序比较简单,有兴趣的读者可以查阅ARM公司的《AMBA Specification》(Rev 2.0)。因为此SPI模块支持3种DMA操作,所以除标准APB信号线外,还有3根与DMA模块连接的请求信号线。

(2)SPI总线接口及时序

SPI总线包括1根串行同步时钟信号线以及2根数据线。

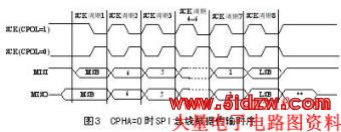

SPI模块为了和外设进行数据交换,根据外设工作要求,其输出串行同步时钟极性和相位可以进行配置,时钟极性(CPOL)对传输协议没有重大的影响。如果CPOL=0,串行同步时钟的空闲状态为低电平;如果CPOL=1,串行同步时钟的空闲状态为高电平。时钟相位(CPHA)能够配置用于选择两种不同的传输协议之一进行数据传输。如果CPHA=0,在串行同步时钟的第一个跳变沿(上升或下降)数据被采样;如果CPHA=1,在串行同步时钟的第二个跳变沿(上升或下降)数据被采样。SPI主模块和与之通信的外设间时钟相位和极性应该一致。SPI接口时序如图3、图4所示[4]。

2.2 SPI模块功能设计

根据功能定义及SPI的工作原理,将整个IP分为8个子模块:APB接口模块、时钟分频模块、发送数据FIFO模块、接收数据FIFO模块、状态机模块、发送数据逻辑模块、接收数据逻辑模块以及中断形成模块。

深入分析SPI的四种传输协议可以发现,根据一种协议,只要对串行同步时钟进行转换,就能得到其余的三种协议。为了简化设计规定,如果要连续传输多个数据,在两个数据传输之间插入一个串行时钟的空闲等待,这样状态机只需两种状态(空闲和工作)就能正常工作。相比其它设计,在基本不降低性能的前提下,思路比较精炼、清晰。

此SPI模块有两种工作方式:查询方式和DMA方式。查询方式通过处理器核监视SPI的状态寄存器来获知其所处的状态,从而决定下一步动作。DMA方式由DMA模块控制数据在内存和SPI间的交换,而不需要处理器核的参与,有效提高了总线利用率。

3 EDA软件仿真与FPGA验证

为了保证设计的鲁棒性,运用多种方法对此IP的功能进行了全面的仿真和验证。

首先进行EDA软件仿真验证。这种仿真包括RTL级和门级仿真验证。RTL级仿真只是将代码文件调入硬件描述语言的仿真软件进行功能仿真,检查逻辑功能是否正确。门级仿真包括布局布线前和布局布线后仿真。布局布线后仿真,可以获得比较精确的时延参数,能够比较真实地反映芯片制造完成后,模块在实际工作中的行为与性能,所以通过了此类仿真就认为模块设计成功,可以进行流片。将RTL级代码转换成门级网表,使用的是Synopsys公司的综合工具DC(Design Compiler)以及台湾集成电路制造公司(TSMC)的0.25μm标准单元库。