标签:嵌入式系统开发,嵌入式开发,http://www.5idzw.com

MPC850嵌入式通信开发平台的硬件设计,http://www.5idzw.com

【摘 要】 介绍了基于PowerPC内核的嵌入式通信控制器芯片MPC850,及一种开发MPC850通信功能的硬件平台设计。<--摘要CH(结束)←-->

<--→关键CH(开始)--> 关键词:嵌入式系统,MPC850,硬件开发平台

从图中可以看出,通信处理器模块CPM支持7个串行信道,包括:2个串行通信控制器SCC,2个串行管理控制器SMC,1个USB接口,1个I2C和1个串行外设接口SPI。因此,MPC850通过灵活的编程方式可实现对Ethernet、USB、T1/E1等的支持,以及对IEEE802.3/Ethern-et、UART(同步/异步)、HDLC、Transparent、App-leTalk、IrDA等多种通信模式/协议的支持。

另外,MPC850还具有增强型在片仿真调试功能,功能齐全的接口单元,可进行优先级编程的中断控制等特征。本系统正是基于MPC850的这些特点来进行通信开发平台的硬件设计的。

2 系统硬件总体设计

设计MPC850多功能通信开发平台的底层,在硬件方面需要提供全面的通信接口、足够的内存容量、调试功能以及测试显示功能。根据设计,本系统主要由CPU、存储器、通信接口、调试以及测试显示等几部分组成。

CPU部分的设计包括了系统的硬件启动与复位、MPC850总线信号分配与定义等。存储器部分包括SDRAM、FLASH ROM和E2PROM。通信接口部分提供了2个Ethernet接口、2个RS232接口、1个RS485接口、1个USB接口、ISDN用户开发板接口以及ATM UTOPIA接口。另外,还提供了MPC850 BDM调试口以及测试口、LED显示等。

3 系统的硬件启动与复位

MPC850的复位方式包括:上电复位、外部/内部Hard Reset、外部/内部Soft Reset、调试口的Hard Reset等。这些方式都由Reset控制器处理。本系统采用了上电复位和外部Hard Reset的方式。

上电复位的过程由芯片内部完成,MPC850需要确认 信号,然后对MODCK〔1-2〕引脚信号进行采样,直到所有的内部PLL(Phase-Locked Loop)进入锁定状态,激活系统时钟,最后,

信号,然后对MODCK〔1-2〕引脚信号进行采样,直到所有的内部PLL(Phase-Locked Loop)进入锁定状态,激活系统时钟,最后, 恢复为高电平。MPC850结束上电复位状态后,锁定内部所有PLL,PowerPC内核持续驱动

恢复为高电平。MPC850结束上电复位状态后,锁定内部所有PLL,PowerPC内核持续驱动 和

和 信号,然后从数据总线上采样系统配置信息。Core在

信号,然后从数据总线上采样系统配置信息。Core在 有效时,也将声明

有效时,也将声明 信号有效。MPC850在处理完毕所有的启动或复位过程后进入正常的系统软件初始化状态,运行上层程序。

信号有效。MPC850在处理完毕所有的启动或复位过程后进入正常的系统软件初始化状态,运行上层程序。

MPC850在从数据总线上采样硬件复位配置字信息的过程中, 信号必须低电平有效;如果

信号必须低电平有效;如果 为高电平,系统就以内部的默认值作为硬件复位配置字。当

为高电平,系统就以内部的默认值作为硬件复位配置字。当 处于有效期间,Core以默认值0x000000000作为配置字。

处于有效期间,Core以默认值0x000000000作为配置字。

4 存储器设计

MPC850中存储器管理器负责控制管理GPCM和UPMs两种存储器控制机制,针对不同的存储器提供灵活的时序支持和无缝连接。其中,GPCM提供了一种简单的、不支持突发方式的低层次的存储器资源和内存映射接口,因此,GPCM控制的内存槽主要用于系统的启动和不支持突发方式的数据存取。而UPM方式支持突发方式,同时包括外部总线的地址复用、周期定时以及DRAM器件可编程的行列地址选通信号的产生,因此,UPM多用于支持高性能的实时存储器。

在本系统的存储器设计中,采用了1片Intel公司的FLASH ROM 28F320J5,2片SAMSUNG公司的SDRAM K4S281632B。其中,BANK0用于FLASH ROM,对应于 片选信号,内存管理机制选择GPCM,数据总线宽度为16-bit;BANK1用于SDRAM,对应于

片选信号,内存管理机制选择GPCM,数据总线宽度为16-bit;BANK1用于SDRAM,对应于 片选信号,内存管理机制选择UPMA,数据总线宽度为32-bit。另外,使用了1片E2PROM 24C02来存放临时数据,接口用I2C总线。

片选信号,内存管理机制选择UPMA,数据总线宽度为32-bit。另外,使用了1片E2PROM 24C02来存放临时数据,接口用I2C总线。

FLASH ROM的容量设计为32Mbit,用来存放实时操作系统和用户应用程序。对BYTE#(ByteEnable)管脚的设置,可以使28F320J5工作在×8或×16模式。

SDRAM的读写以及突发模式的时序控制通过对MPC850 编程来实现,时钟由

编程来实现,时钟由

MPC850 ,MPC850嵌入式通信开发平台的硬件设计

,MPC850嵌入式通信开发平台的硬件设计

【摘 要】 介绍了基于PowerPC内核的嵌入式通信控制器芯片MPC850,及一种开发MPC850通信功能的硬件平台设计。<--摘要CH(结束)←-->

<--→关键CH(开始)--> 关键词:嵌入式系统,MPC850,硬件开发平台

<--关键EN(结束)←-->1 MPC850简介

Motorola公司的MPC850通信控制器芯片基于PowerPC内核,以精简指令集计算RISC的体系结构为基础,集成了32位微处理器和多种外设接口,具有强大的通信和网络协议处理能力,可广泛应用于各种通信和网络产品,如ADSL modem、SOHO路由器、低速ISDN、T1/E1终端、ATM线卡控制、局端交换、无线接入等。

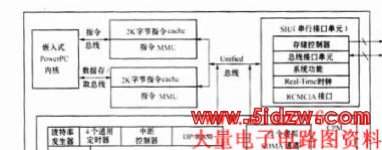

MPC850的功能结构主要包括:嵌入式PowerPC内核,系统接口单元(System InterfaceUnit,SIU)和通信处理器模块(Communications Processor Module,CPM)。其体系结构的框图如图1所示。

从图中可以看出,通信处理器模块CPM支持7个串行信道,包括:2个串行通信控制器SCC,2个串行管理控制器SMC,1个USB接口,1个I2C和1个串行外设接口SPI。因此,MPC850通过灵活的编程方式可实现对Ethernet、USB、T1/E1等的支持,以及对IEEE802.3/Ethern-et、UART(同步/异步)、HDLC、Transparent、App-leTalk、IrDA等多种通信模式/协议的支持。

另外,MPC850还具有增强型在片仿真调试功能,功能齐全的接口单元,可进行优先级编程的中断控制等特征。本系统正是基于MPC850的这些特点来进行通信开发平台的硬件设计的。

2 系统硬件总体设计

设计MPC850多功能通信开发平台的底层,在硬件方面需要提供全面的通信接口、足够的内存容量、调试功能以及测试显示功能。根据设计,本系统主要由CPU、存储器、通信接口、调试以及测试显示等几部分组成。

CPU部分的设计包括了系统的硬件启动与复位、MPC850总线信号分配与定义等。存储器部分包括SDRAM、FLASH ROM和E2PROM。通信接口部分提供了2个Ethernet接口、2个RS232接口、1个RS485接口、1个USB接口、ISDN用户开发板接口以及ATM UTOPIA接口。另外,还提供了MPC850 BDM调试口以及测试口、LED显示等。

3 系统的硬件启动与复位

MPC850的复位方式包括:上电复位、外部/内部Hard Reset、外部/内部Soft Reset、调试口的Hard Reset等。这些方式都由Reset控制器处理。本系统采用了上电复位和外部Hard Reset的方式。

上电复位的过程由芯片内部完成,MPC850需要确认

MPC850在从数据总线上采样硬件复位配置字信息的过程中,

4 存储器设计

MPC850中存储器管理器负责控制管理GPCM和UPMs两种存储器控制机制,针对不同的存储器提供灵活的时序支持和无缝连接。其中,GPCM提供了一种简单的、不支持突发方式的低层次的存储器资源和内存映射接口,因此,GPCM控制的内存槽主要用于系统的启动和不支持突发方式的数据存取。而UPM方式支持突发方式,同时包括外部总线的地址复用、周期定时以及DRAM器件可编程的行列地址选通信号的产生,因此,UPM多用于支持高性能的实时存储器。

在本系统的存储器设计中,采用了1片Intel公司的FLASH ROM 28F320J5,2片SAMSUNG公司的SDRAM K4S281632B。其中,BANK0用于FLASH ROM,对应于

FLASH ROM的容量设计为32Mbit,用来存放实时操作系统和用户应用程序。对BYTE#(ByteEnable)管脚的设置,可以使28F320J5工作在×8或×16模式。

SDRAM的读写以及突发模式的时序控制通过对MPC850

MPC850