数字量变换器是一种多路数据采集设备,主要采集各传感器的输出信号(及其他需经遥测系统传送的信号),将各路信号按一定体制组合起来并加上帧同步码形成一定格式的PCM数据,互不干扰地通过同一个信道传送出去。

PCM解码板是为数字量变换器设计的接收端,把组合信号解调出来,恢复各路原始信息,加以记录、处理和显示,用于数字量变换器的单机调试和单元测试。限于测试台空间的严格要求以及测试系统的微型化、高速数据传输、低功耗原则,PCM解码板采用了基于低压差分信号LVDS的串行通信技术增强了抗噪声、抗干扰能力,并以时钟和数据恢复技术解决了限制数据传输速率的信号时钟参差问题,大大提高了数据传输的数据率。选用了FPGA作为PCM解码板控制核心,将各功能模块由FPGA统一协调完成,从而简化了设计的复杂程度,缩短了试验和开发周期。

1 模块硬件结构

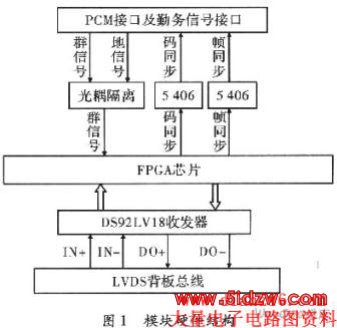

PCM解码板硬件结构,如图1所示。

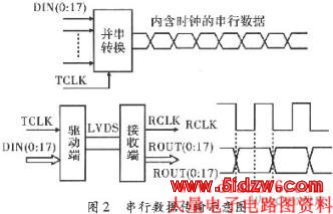

PCM解码板接收到上位机上传PCM数据命令后,输出帧同步信号给数字量变换器,并接收数字量变换器输出的PCM串行数据,在码同步信号的配合下,将PCM串行数据经FPGA串并转换后写入FPGA中的发送FIFO(First In First Outmemory先进先出存储器)中。LVDS总线物理层将FPGA中的FIFO内数据包的数据和时钟信号编码为20位串行数据上传。串行数据传输示意图,如图2所示,TCLK为发数时钟,RCLK为解串时钟。

2 LVDS总线结构

针对数据可靠传输在数据交换系统中的重要性,方案结合LVDS接口和OSI网络模型,设计了一种基于LVDS接口的数据传输协议,并具体给出了各协议层所实现的功能及协议约束关系。基于LVDS的总线体系结构大致分为:物理层、数据链路层和传输层。

(1)物理层。

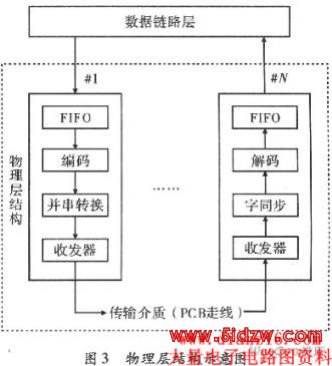

LVDS总线采用DS92LVl8专用接口芯片,连接构成两对LVDS信号,一对用于发送,一对用于接收。物理层在发送端将时钟信号用18 bit/20 bit编码方案嵌入数据中以达到高速数据率;在接收端将串行数据流中的数据和时钟分离,然后对串行数据进行采样,从而在接收端恢复了串行数据。通过搜寻同步字符进行字同步,数据流恢复到和发送端编码后的数据流相同,该数据流再经解码,恢复原始数据,写入接收端的FIFO内,等待数据链路层的进一步处理。

物理层除了收发器(DS92LV18芯片)和传输介质(PCB走线)外的所有模块均在FPGA中实现。物理层结构示意图,如图3所示。

LVDS两对低压差分信号无论其传输介质是电缆还是PCB走线,都必须与终端匹配,以减少不希望的电磁辐射,提供最佳的信号质量。通常一个尽可能靠近接收端的100 Ω终端电阻跨在差分线上即可提供良好的匹配。电路设计中,输入差分线对离开DS92LV18集成芯片后立刻尽可能地相互靠近(距离<10 mm),以保持接收器的共模抑制能力,并且两条差分线之间的距离应尽可能保持一致,以避免差分阻抗的不连续性,这样能减少反射并能确保耦合到的噪声为共模噪声。

(2)数据链路层。

在数据链路层中包含控制逻辑和帧格式,数据以帧为单位传送,在目的节点被接收。这样做是为了当出现差错时,可将有错误的帧重传一次,从而避免了将全部数据都重传一次所带来的带宽浪费,且各接收节点能从接收到的比特流中明确地区分出一帧的开始和结束在什么地方,以及数据和控制信息。该层的功能模块也在FPGA中实现。

(3)传输层。

传输层的任务是为从发送节点到目的节点提供可靠、合理的信息传输。传输层是控制通信过程的核心,初始化和通信过程中,需要设置必要的计时器、地址和状态寄存器,这些都是传输层来实现。其中,地址寄存器用于存储节点前继和后继地址,计时器是为初始化和通信过程中的超时报警而设置。该层功能可通过在FPGA内部定义信号来实现。

3 PCM码解调设计

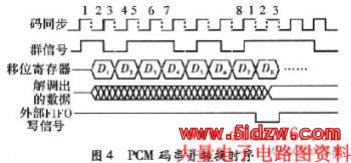

PCM解码部分用于接收数字量变换器输出的PCM串行数据并将数据串并转换。该部分需产生两种勤务信号,帧同步信号:周期为25 ms,码宽8μs;码同步信号:频率81.92 kHz,占空比50%,用于数字量变换器内部的时序控制。每8个一组的码同步信号称作一路,在每帧中从第1路开始排到128路结束。模块接收的群信号是串行“0”“1”码,为不归零码。PCM解码部分工作原理:根据帧、码同步信号时序特征,FPGA生成一个数据时序进程,在时钟信号的推动下通过地址推进来输出帧、码勤务信号。数字量变换器输出的串行PCM数据流在码同步信号作用下,通过移位寄存器转换为8位并行数据,通过写信号WR同步将解得的并行PCM码写入到FIFO中。串并转换的工作时序,如图4所示。

经多次测试,上位机读回的数据按照副帧结束标志EB 90两个bit和帧结束标志14 6F两个bit所组成数据格式的结果与设计要求吻合。

4 结束语

实践表明:由于采用低压差分信号传送数据,不易受共模噪音影响,可以实现更快的数据传输,同时具有低功耗、低噪声等优良特性;由于总线结构物理层可以采用专用接口芯片实现,而数据链路层和传输层均可采用可编程逻辑器件FPGA实现。因此,总线硬件实现简单,易于低成本解决系统高速通信问题。通过测试分析,该板在PCM解码的抗干扰能力及实现解码数据的高速、可靠传输方面均达到了系统提出的技术指标。

,基于LVDS接口的PC M解码板设计