摘要:包含2线总线(例如:I2C或SMBus)的应用需要在上升时间、电源损耗、噪声抑制等参数之间做出折中。这种漏极开路总线从低电平跳变到高电平的上升时间由上拉电阻和总线电容决定,因此,在增加外设、布线长度和连接器时,很难保持干净快速的上升沿。为了解决上升时间问题,本应用笔记提出了一种上升时间加速电路,用一种简单方式加速上升沿,提高噪声抑制并降低功耗。

电路描述

在某些2线总线应用中,选择适当的上拉电阻即可提供足够快的上升时间,并在可接受的功耗下获得良好的噪声抑制。但是,对于总线电容较高的大型系统或者是功率受限的便携系统,可能需要有源电路为漏极开路信号提供更短的上升时间。

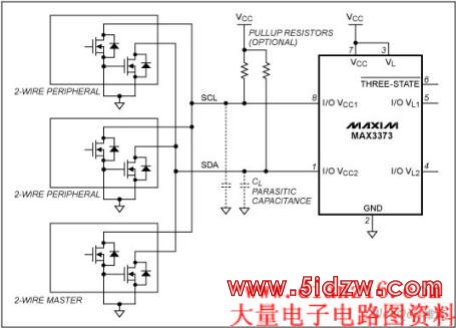

图1给出了利用MAX3373设计的上升时间加速电路,有助于提高噪声抑制并保持最低功耗。这里利用了MAX3373低压电平转换器的上升时间加速功能,而非电平转换功能。当IC检测到某个I/O引脚的电压升高时,将在短时间内打开内部强上拉电路(pFET管),快速对总线寄生电容充电。经过很短的时间,加速电路关闭,仅由内部10kΩ上拉电阻保持逻辑高电平。

图1. MAX3373利用上升时间加速电路快速驱动总线的大电容。

性能*估

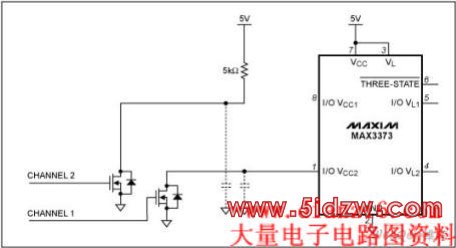

图2电路用于测试MAX3373作为上升时间加速器的性能,其中分立漏极开路FET同时驱动两条独立线路。通道1由MAX3373加速,通道2简单地由上拉电阻和寄生电容端接(两条线路具有相同电容C)。MAX3373的等效上拉电阻仅为5kΩ,因为它的输入和输出端(I/O VCC和I/O VL引脚)包含10kΩ内部上拉电阻。下面给出了110pF电容(图3)和I?C总线最大允许电容400pF (图4)时的结果。(请注意这些图中时间刻度的不同。)

图2. 该电路用于*估MAX3373的上升时间与电容、时钟速率的关系。通道1利用MAX3373加速上升时间,通道2的上升时间由上拉电阻和寄生电容决定。 通过测试2线总线的常用时钟速率:100kHz和400kHz,可以看出MAX3373所具备的优势。100kHz时钟对应周期为10μs,高电平仅为5μs。这样,110pF电容和5kΩ上拉电阻的上升时间约1.25μs,仅占周期的12% (图3)。在这种条件下,不需要加速上升时间就能得到可接受的指标。

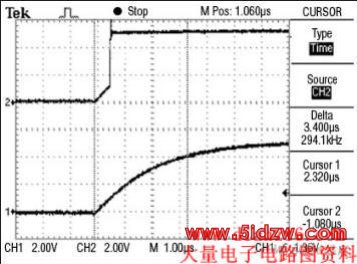

图3. MAX3373电路(通道1)与非加速电路(5kΩ上拉、100kHz时钟和110pF寄生电容) (通道2)的对比。 寄生电容为400pF时,上升时间约4μs,占周期的40%,这对于多数100kHz系统是不可接受的。在400pF系统中使用MAX3373,上升到最大值90%的时间可以达到500ns,仅为10μs周期的5% (图4)。

图4. MAX3373电路(通道1)与非加速电路(5kΩ上拉、100kHz时钟和400pF寄生电容) (通道2)的对比。

对于400kHz总线(周期为2.5μs,高电平为1.25μs),上述条件中的5kΩ电阻和110pF电容可提供1.25μs的上升时间,占周期的50%,通常无法接受这样的上升时间;将电容加大至400pF,上升时间将达到5μs,即时钟周期的两倍,这对于系统来说完全不可接受。而使用MAX3373电路,在110pF负载电容下上升到最大值90%的时间约为250ns,仅为2.5μs周期的10%;400pF负载电容下,上升时间仅为500ns,是周期的20%。

结论

使用MAX3373作为上升时间加速器是解决2线总线上升时间与时钟问题的方法之一。某些情况下,可以简单地通过降低上拉电阻来加速上升时间。而MAX3373提供了一种简单的加速上升时间的方法,有助于提高噪声抑制并使功耗最低。

,2线总线上升时间加速电路