摘要:本文以Lattice公司的ispLSI系列器件为例,介绍了系统内可编程(ISP)及其使用方法

关键词:可编程逻辑器件(PLD) 数字系统 ispLSI

ispLSI系列器件

PLD器件自70年代发明发来,从熔丝型发展到光可擦除型;到80年代发展成为电可擦除型;到90年代,美国Lattice半导体公司开发出采用ISP(在系统内编程)技术的PLD――ispLSI系列。该系列器件集成度1000~25000门,引脚到引脚延时最小可达3.5ns,系统工作速度最高可达180MHz。器件具有在系统内可编程(ISP,In-System Programmable)能力和边界扫描测试能力,适合在计算机、仪器仪表、通信、雷达、DSP系统和遥测系统中使用。ISP技术可以使用户具有在自行设计的目标系统中对逻辑器件进行编程或者反复改写。ISP技术为用户提供了传统技术无法达到的灵活性,可以大大缩短电子系统设计周期,简化生产流程,降低生产成本,并可在现场对系统进行逻辑重构和升级。ISP技术使硬件随时能够改变组态,实现了硬件设计的软件化。

Lattice公司的ispLSI器件既有PLD的性能和特点,又有现场可编程逻辑阵列(FPGA)的高密度和灵活性。它强有力的结构能够实现各种逻辑功能,其中包括寄存器、计数器、多路选择、译码器和复杂状态机等,能够满足对高性能系统逻辑的需求,广泛地适用于各个领域。

目前Lattice公司生产的ispLSI器件分为6个系列:ispLSI1000/E系列,ispLSI2000/E/V/VE系列,ispLSI3000系列,ispLSI5000V系列,ispLSI6000系列和ispLSI8000系列。这六个系列的器件在用途上有一定的侧重点,所以在结构和性能上存在细微的差异,有的速率快,有的密度高,有的成本低,适用对象具有针对性。在使用时,应当根据各系列器件的特点和适用范围来选择。

iapLSI器件的编程方便简单,使用ISP编程电缆和下载的ISP软件就可以完成编程工作。在连接时,编程电缆一端连接在电脑的并口上,一端连接在被编程器件所在电路板的ISP接口上。为配合其PLD的使用和开发,Lattice公司推出的数字系统设计软件为ispEXPERT,设计输入可以采用原理图、硬件描述语言和混和输入三种方式。它能对所设计的数字电子系统进行功能仿真和时序仿真的设计检验,能对设计结果进行逻辑优化,将逻辑映射到器件中去,自动完成布局并生成编程所需要标准的熔丝图JED编程文件。最后可以随时通过连接电缆,将编程文件下载到器件中去。

编程过程分三步:1.按地址和命令将JED文件中的数据自串行输入端(SDI)输入数字寄存器;2.将编程数据写入E2CMOS逻辑单元;3.将写入的数据自串行输出端(SDO)输出进行校验。

ispLSI器件设计应用实例

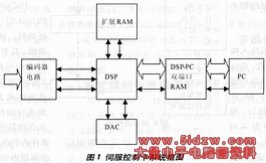

本文使用基于PC的六轴伺服控制卡作为设计实例,采用TI公司的DSP(数字信号处理器),TMS320F240为工作核心微处理芯片,包括光电编码器输入模块、数模转换电路模块,DSP-PC通信双口RAM模块和扩展RAM模块(见图1)。光电编码器输入模块中包括六路数字滤波电路、四分频、鉴相电路、16位可逆计数器电路、输出缓冲/锁存器电路、选通电路。这一模块各部分电路中,大部分都为数字电路。由于是六路输入,因此需要的逻辑器件数目很多。采用传统数字电路,例如TTL和CMOS器件设计的系统,电路复杂,板块庞大,实际可行性不大。为此,在系统中使用了Lattice公司的ispLSI系列CPLD(复杂可编程逻辑器件),来实现这一部分数字电路和逻辑控制。

1.器件的选择

编码器模块电路总共使用I/O管脚数目为97个,大约需要30~40个GLB单元。选用ispLSI3256A-90LM芯片来实现六路光电编码输入模块电路。它的集成度为11000门,具有128个I/O引脚,384个寄存器,48个GLB单元,管脚延迟为12ns,系统速度为90MHz,从资源和速度上能够满足这个六轴伺器控制卡的需求。

2.设计输入方法

由于六路光电编码器输入模块电路的分模块较多,因此,设计输入方法主要采用Lattice公司提供的数字系统设计软件ispEXPERT绘制原理图设计。根据各个模块的不同,分别采用ABEL语言编写测试向量,和绘制测试输入波形的方法,完成仿真测试。使用Lattice提供的编程板完成对器件的编程。

3.结构设计

由于电路模块多,于是采用层次化设计。设计时,建立一个顶层文件,其中描述各个逻辑模块、接口和模块之间的连接关系说明以及管脚分配。各个单元模块,建立为自定义元件。数字滤模块由D触发器、JK触发器和逻辑门搭成。监相电路使用系统库中逻辑门元件搭成。产生正负计数脉冲,用于可逆计数器计数。

每路信号需要通过16位可逆计数器, 对编码器的信号进行计数,计数结果保留在计数器内。16位可逆计数器模块采用系统元件库中的2个带有输出锁存的8位可逆计数器GBUD8宏模块搭成。直接选取系统宏单元模块,可以减少设计工作量,节省GLB单元空间,资源利用率高。由于ispLSI器件的特点要求,采用多路开关DMUX82作为选通方式。

对编码器的信号进行计数,计数结果保留在计数器内。16位可逆计数器模块采用系统元件库中的2个带有输出锁存的8位可逆计数器GBUD8宏模块搭成。直接选取系统宏单元模块,可以减少设计工作量,节省GLB单元空间,资源利用率高。由于ispLSI器件的特点要求,采用多路开关DMUX82作为选通方式。

选用两个8位三态输出门OT38输出16位数据。

结构设计过程中,以逻辑单元、库元件为单位如逻辑门、寄存器、计数器等,选择适用的库元件完成电路,而有别于传统器件设计方法以元器件为单元。设计更为直接简单。在设计中可以同时完成仿真工作,不需要另搭接电路板进行仿真试验。

PLD设计流程

通过应用总结设计流程如下:

1.设计准备:首先定义I/O端口,目的是选择合适的器件。然后进行逻辑划分,按电路形式划分为若干模块,尽量以宏单元模块方式进行划分。

2.设计输入:由设计者对器件的逻辑功能进行描述,可以用原理图方法,也可以用HDL硬件描述语言(如ABEL-HDL,CUPL和MINC-HDL语言)来输入。

3.设计实现:将设计输入文件进行编译最后生成熔丝图。包括优化、合并、映射、布局、嘏线和数据文件生成六步。

4.器件编程:设计编译好后,将数据文件下载到可编程器件中。IspLSI器件可在线路板上编程;也可以在专用编程器上编程。

5.设计校验:在设计过程中,同时进行校验过程。包括了功能仿真、时序仿真和器件测试。

其设计流程图如图2所示。

PLD性能评价

E2CMOS工艺和ISP技术结合的ispLSI器件有高逻辑密度、低功耗,擦除和改写时间为秒数量级,具有100%的参数可测试性和100%的编程和功能正确率。E2CMOS工艺的非易失性意味着在掉电或上电后不需要对器件重新进行编程,另外它无需采用附加存储器件来保存逻辑组态数据。器件内的保密位,可以防止对器件内编程内容的非法复制。商业级的可编程逻辑器件在0~70℃范围内,均可进行编程,至少可以保证1000次编程或者擦除,以及20年的编程数据保持期。