摘要: 介绍了采用Videx-ⅡPR0系列FPCA设计的应用于下一代无线通信系统中的高速I/O。由于充分利用芯片中集成的Rocket I/O模块,并采用差分输入参考时钟、8B/10B编码、预加重处理、通道绑定技术等,实现了四个绑定通道的高速互连(2.5Gbaud)。设计结果表明,采用Rocket I/O模块进行高速I/O设计,可极大简化片上逻辑电路和片外PCB版图设计。

关键词: Rocket I/O 抖动 差分线 通道绑定 眼图

由于通信对带宽的需求迅猛增长,促使一系列基于差分、源同步、时钟数据恢复(CDR)等先进技术的互连方式应运而生。在传统设计中,单端互连方式易受干扰、噪声的影响,传输速率最高只能达到200~250Mbps/Line;在更高速率的接口设计中,多采用包含有源同步时钟的差分串行传输方式(如LVDS、LVPECL等),但在传输过程中时钟与数据分别发送,传输过程中各信号瞬时抖动不一致,破坏了接收数据与时钟之间的定时关系,因而传输速率很难超越1Gbps/Channel;XILINX公司推出了内嵌Rocket I/O模块的VirtexⅡPRO系列FPGA,使实现更高的传输速率成为可能[1~3]。采用了CML(CurrentMode Logic)、CDR、线路编码(8B/10B)和预加重等技术的Rocket I/O模块,可极大地减小时钟扭曲、信号衰减和线路噪声对接收性能的影响,从而使传输速率进一步提高。本文着重讨论如何配置Rocket I/0模块,进行FPGA的片内、片外设计和仿真,从而在以10英寸差分线组互连的两片FPGA间达到2.5Gbaud/Channel的传输速率,并实现了四个双向通道的绑定操作。

图1

1 Rocket,I/O特性

VirtexⅡPRO系列FPGA内嵌的Rocket I/O模块是基于Mindspeed公司四代SkyRailTM技术开发的高速串行收发器,该系列FPGA单片最多集成了24路Rocket I/O收发器,最大可提供75Gbps全双工通信带宽。Rocket I/O模块灵活的配置方式使其可以提供对光纤通道、千兆以太网、XAUI、Infiniband、PCI Express等一系列高速通信标准的支持。其主要特性为:(1)每个通道收发器支持从622Mbps至3.125Gbps的全双工传输速率;(2)收发器内嵌发送时钟生成电路和接收时钟恢复电路;(3)CDR源同步数据发送方式;(4)五级可编程输出电压幅度(800~1600mV)控制;(5)四级可编程输出预加重处理;(6)收发器支持交流和直流耦合方式,可兼容多种高速接口标准;(7)片内集成可编程差分终端电阻(50Ω、75Ω);(8)支持片内串行和并行环回测试模式;(9)可编程标界检测符(comma)图样,提供对多种协议标准的支持。

Rocket I/0收发器由物理媒质适配层(PMA)和物理编码子层(PCS)构成,如图1所示。其中PMA层属于收发器的数/模混和部分,包括串/并变换器、并/串变换器、差分发送驱动器、差分接收器、发送时钟生成电路、接收时钟恢复电路等。而PCS层属于收发器的数字部分,包括发送FIFO、8B/10B编码器、8B/10B解码器、CRC生成和校验、用于通道绑定和时钟修正的Elastic Buffer等。由于要支持多种高速串行通信标准,Rocket I/O模块的PMA和PCS包含了许多配置参数,这些参数可以通过外部端口和内部配置寄存器进行设定。配置过程可以以静态(参数通过FPGA配置文件设定)或动态(通过Rocket I/O的配置端口进行局部重新配置)的方式进行。

2 ROCket I/O的设计要素

要达到Rocket I/O模块的最佳性能,需要考虑到诸多设计因素,本文就其最重要的部分展开讨论。

2.1 参考时钟

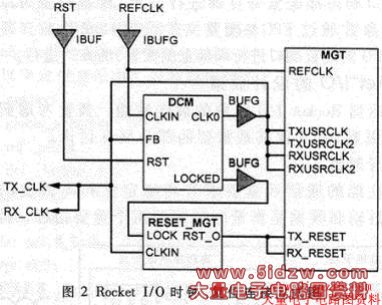

高性能的通信质量要求有高稳定性和高精度的时钟源。抖动和频偏是衡量时钟源的两个重要指标。抖动一般是指一个实际情况下的周期信号每个周期的图样相对于该信号理想情况下一个周期图样的偏差[4]。抖动产生原因包括时钟晶体本身的机械振动、器件的热噪声和电源串人噪声等。抖动可以分为确定性抖动和随机抖动。确定性抖动是线性可加的,它包括信号在传输中媒质损耗、码间串扰(ISI)等周期性因素导致的抖动;随机抖动是均方可加的,它是由半导体器件热噪声、电源波动等共模随机噪声源导致的。频偏是指时钟标称频率与实际频率的偏差,主要受晶体加工精度的影响。由于Rocket I/O模块内部将输人参考时钟20倍频,而RocketI/O模块可容忍的输人参考时钟抖动公差为40ps,可见参考时钟的抖动对其性能有直接影响。在VirtexⅡPRO系列FPGA中,Rocket I/O模块集中分布在上、下四个通道中。当Rocket I/O工作在2.5Gbaud以上时,参考时钟应采用差分输入方式(如LVDS、LVPECL),由上、四个通道的专用差分时钟引脚输入,至相同或相邻通道中Rocket I/O的BREFCLK输入端,以避免时钟信号引入不必要的抖动。在2.5Gbaud速率以下应用时,不要用FP-GA内的DCM来生成Rocket I/O的输入时钟, 因为经DCM倍频的时钟会引入较大的抖动,使Rocket I/0的接收锁相环无法稳定地锁定发送时钟。图2所示的连接方案中,Rocket I/O模块的输入时钟由差分或单端引脚馈入后,应只经过一级全局缓冲(BUFG)布设到时钟树上,再连接到Rocket I/O模块的参考时钟输入端,这样可最大限度地降低抖动的引入。

2.2 复位

Rocket I/O模块的复位引脚分为发送(TX_RESET)和接收(RX_RESET)两部分。由于DCM在输出时钟锁定在设定值前,输出时钟处于不稳定状态,不能用作内部逻辑电路时钟,所以要在DCM时钟输出锁定有效,并经过适当延迟后才可将片内逻辑复位。Rocket I/O模块要求复位输入至少保持两个USRCLK时钟周期来完成FIFO的初始化[1]。如图2所示,图中RESET_MGT模块实现的即是上述功能。

2.3 8B/10B线路码

线路码具有平衡码流中“0”、“1”概率的能力,并且可以减小码流中长连“0”和长连“1”串。8B/10B编码是属于基于块编码的mBnB线路码中的一种。经过mBnB编码的码流具有“0”和“1”等概率、连“0”和连“1”数小、直流基线漂移小、低频分量小、功率谱带宽较窄、时钟成分丰富、定时提取方便且抖动小以及能进行运行误码监测等许多优点,因此在Rocket I/O模块内部集成了8B/10B编码器和解码器。

应用Rocket I/0模块进行互连时,根据互连双方接口的电气标准的不同,分为直流耦合和交流耦合方式。在直流耦合方式下,并不一定要求采用8B/10B编码,可以选择其它的线路码型或不用线路编码。但在较高的传输速率条件下(如2.5Gbaud以上),为了达到良好的抗干扰性能和低的误码率,应该考虑采用8B/10B编码。而在交流耦合方式下,必须选择8B/10B编码,否则接收端的漂移会使接收器无法正常工作。

8B/10B编码集合中包括数据字串部分和控制字串部分[1]。数据字串包括256个可能的数值,其中包括可作为控制字串(K23.7、K28.0~K28.7、K27.7、K29.7、K30.7)的码字。当传送字串作为控制字时,由Rocket I/O模块相应的控制字标志输入引脚(如TX_CHARISK)指定该字为控制字串。

2.4 通道绑定

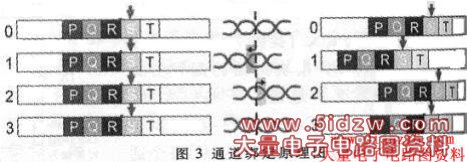

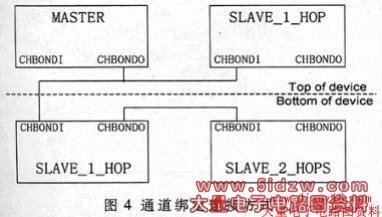

通道绑定是指将多个串行通道组合在一起构成一个并行通道,以此来提高收发的数据吞吐率。由于每个通道在收发器互连、时钟再生和数据接收延迟上各不相同,会使接收到的数据产生“错位”的情况(如图3所示), 因此要在发送端数据流中加入一个特殊的序列――通道绑定序列,如图中的“P”字符。每个绑定通道都设定“P”字符为通道绑定序列,在接收端指定一个通道为主通道,其余通道都依据主通道的CHBONDO有效指示进入绑定状态,进而锁定本通道在Elastic Buffer中接收到通道绑定序列的位置。由Elastic Buffer向内部逻辑电路输出数据时,所有经过绑定的通道都以绑定序列指定的Elastic Buffer中的偏移位置进行对齐输出。通道绑定完成后,为了使绑定维持在稳定状态,各通道收发器也要以主通道收发器为基准进行时钟修正操作。

,基于Rocket I/O模块的高速I/O设计