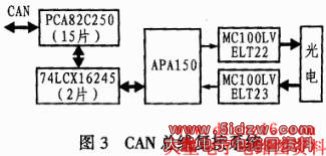

ժҪ��APA150��Actel��˾�Ƴ��ĵڶ�������Flash�Ŀɱ��FPGA����ϵ��ProASIC Plus�е�һ�֣��dz��ʺ����ASIC���ں��ա����ѵ��ӡ���ҵ���ơ������ͨ���г������½�����APA150����Ҫ�ص㡢�ڲ��ṹ����Ҫ���ܲ�����������APA150��ͨ��ϵͳ����е�Ӧ��ʵ����

�ؼ��ʣ�APA150 FPGA ASIC Flash

��������

���У��������ǣ������칫˾�Ƴ��ĵڶ������ڣƣ���裨���棩�Ŀɱ�̣ƣУǣ����ƣ���� �У����������� �ǣ���� ����������ֳ��ɱ�������У������У����ӣɣ� �У����ϵ���е�һ�֡���ϵ��������ߣ��ӣɣã�ר�ü��ɵ�·�������ܺͣƣУǣ����������һ������ˣ��ɷdz����õ������-�ӣɣ����ں��ա����ѵ��ӡ���ҵ���ơ������ͨ���г����У����ӣɣ� �У����ϵ�в�Ʒ����Ҫ�ص����£�

��ϵͳ�ڿ��ظ���̣�

�����ʧ�����ã��������̣����ãͣϣӹ��գ����ãƣ���赥Ԫ�����а�ȫ�ķ���ʧ����洢���ܣ��ϵ缴�����У�����������ãУңϣʹ洢����

��߶ȱ��ܣ�ʹ���߿ɱ�����ö�λ��Կ����ֹ������ж�ȡ��������������ã�

�ĵ͢�оƬ���ĵ�ѹΪ�������֣�

���������ӣɣ����Ƶľ�ϸ�����ܹ���֧�����еģ��ӣɣù������̣���������̲�Ʒ����ʱ�䣬����ת�������ӣɣá�

�����ڲ��ṹ����ԭ��

���У���������Ҫ������Ԫ�顢Ƕ��ʽ�ң��Ϳ顢�ɣ��Ͽ�Ϳɱ�����ߵȼ������ֹ��ɣ������֮���ò�ͬ�ȼ��������ߺͣƣ���迪��������

����Ԫ�ǣУ����ӣɣ� �У���������Ļ�����ɵ�Ԫ������ʵ�ֻ����������ܡ����У��������ڲ��У�������������Ԫ��ÿ������Ԫ����������˺�һ������ˡ�ͨ���ʵ�������ãƣ���迪�ص�״̬���ɽ�����Ԫ���ó�Ϊ������������ġ����������֮������������ܿ飬��������š������������λ�˵���������Ĵ������ȡ��������Ԫ����������ʵ�ָ����ӵ������ܡ�һ��ĸ����Ժ��������ƿ�������Ԫ��ʵ�֣���Ϊ����߹�Ƭ�������ʺ����������ܣ�һЩ��Ϊ���ӵĹ���Ӧͨ����Ƕ������洢��Ԫ����ɡ�

���У���������Ƕ�������������������ģң��Ϳ飨����������������Щ�ң��Ϳ���Էdz������ʵ��һЩ��ģ��̫��ģƣɣƣϡ�˫�˿ڣң��͵ȹ��ܡ�ÿ���ң��Ϳ���������£������֣�

��������������

���������ߣ�������λ�����������ߣ��ڣ�λ����ż����λ��������д����λ��ַ���ߺ�����������ߣ�

����������д���ƣ�����д���Զ����������Ϊͬ�����첽������ʽ������Ӧ��·��Ƶ�����Ժ�ʱ���š�

������Ը������Ҫ������ѵ�����ң��Ϳ飬�Եõ�����Ŀ��Ȼ���ȡ���Ϊ��ЩƬ�ڴ洢���Ķ���д��Ƭ��ң��Ϳ�öࡣ

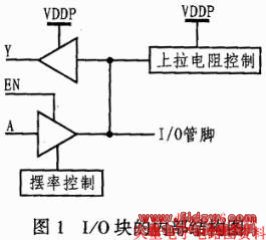

�ɣ��Ͽ���Ҫ�����ṩ�ܽŵ��ڲ��ź��ߵĽӿڢ���������������ĵ������Կ��ơ�ͨ��������ãɣ��Ͽ��ʹ�ɣ��Ϲܽž������롢�����˫�����̬�����ȹ��ܣ����ڲ��ṹ��ͼ����ʾ����������������ӵ�ÿ���ɣ��Ϲܽſ��Է�ֹ�����ڷ���������ʱ�ܽų���������ͨ����������źŵĵ�ѹ���ʿ�������������ת���ٶȵ�Ҫ���罫�֣ģģнӵ���Դ����ô�����֣ģģ�Ϊ��������ʱ�������ѹ������ߵ�ƽΪ�������֣������֣ģģ�Ϊ��������ʱ�������ѹ��Ϊ�������֣��������֣������ƽ���룲�����ֻ�����ϵͳ���ݡ�

���У������������ڲ��鲼һϵ���ĸ�����ˮƽ�ʹ�ֱ�������ߣ����г����ٱ���������������������Ԫ����Ч�������ʵ��Զ������ȳ����ӣ��䳤�ȿ��Կ�Խ������������Ԫ�����⣬���������߳����������������ȳ����ӣ������Կ�Խ����������������ȫ���߳���������ȫ�ֹܽŵ��ڲ�������Ԫ���������ʱ�ӡ���λ�Ĺܽŵȡ�

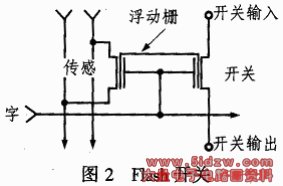

���������������Ԫ�������������״̬���ϵ缴����ϵͳ�ڱ�̵ģƣ���迪������������ṹ��ͼ����ʾ�����У�����դ��������ͨ������ŵ����趨��������������·֮��Ŀ���״̬�����ڿɱ������������δ�����κ������仯�����ͨ�����Ϸ���̽�ⲻ���κν���������仯��ֻ�и���դ�ĵ���������ˣ����ڣƣ����ģ��У������� �Ȳ����������գ��練��˿���ģƣУǣ������Է�����ơ�

�����ܽŹ��ܺ���Ҫ����

������ �ܽŹ���

���У��������ķ�װ��ʽ�У������ţԣѣƣУ������ķ���ƽ��װ���������� �ţУѣƣУ����Ϸ��ͱ�ƽʽ��װ���������� �ţУ£ǣ���������դ���з�װ���Լ����������������ţƣ£ǣ��������դ���У���װ����ʽ��ʹ��ʱ�ɸ�������Ƶ�ϵͳѡ���ʵ��ķ�װ�������ԣ����� �ŵģԣѣƣ�Ϊ��������ܽŹ��ܣ�������������С�

��1 APA150�ĹܽŹ���

| �� �� �� | �� �� �� |

�� �� �� �� |

| VDD | 17,37,68,89 | ��2.5V����ΪоƬ��Դ |

| VDDP | 26,39,40,76,87,100 | ��2.5V��3.3V����ΪI/O������ѹ |

| I/O | 2��8,18��24,27��36,41��46, 57��59,69��74,77��85,90��99 |

���������롢�������̬��˫�壬�����롢���ʱ����TTL��CMOS��ƽ�����õ�����ܽ�Ӧ����λ���� |

| GL | 11,16,60,65 | ȫ�ֹܽţ�����Ϊ��ʱ��ʱ�ӻ�����ȫ���ź����룬Ҳ������Ϊ��ͨI/Oʹ�� |

| NPECL | 13,63 | ���˱�I/O�ڣ�APA150оƬ���ṩ�͵�ѹ���伫�������LVPECL�����IJ��I/O��Ʒ��NPECL��PPECL�ֱ�Ϊ�������������룬���߱ȽϵĽ�������ڲ����������ʱ�ս� |

| PPECL | 15,61 | |

| TMS | 49 | ����ģʽѡ�����ڿ��Ʊ߽�ɨ���· |

| TCK | 47 | ����ʱ�ӣ�ͬʱ�DZ߽�ɨ���ʱ�����루���Ϊ10MHz�� |

| TDI | 48 | �����������룬��Ϊ�߽�ɨ��Ĵ������� |

| TDO | 54 | ���������������Ϊ�߽�ɨ��Ĵ������ |

| TRST | 55 | ���Ը�λ���룬��Ϊ�߽�ɨ����첽��λ�ˣ��͵�ƽ��Ч |

| RCK | 56 | ����ʱ�ӣ����ʱ����ȡ�����ɿ���TCK |

| VPP | 52 | �������Դ����Χ��0��16.5V��Ҳ���Կսӣ�Actel�Ƽ��սӻ�������VDDP |

| VPN | 53 | �������Դ����Χ��0��-13.8V��Ҳ���Կսӣ�Actel�Ƽ��սӻ�ӵ� |

| AVDD | 14,62 | �ڲ������Դ�ţ���2.5V��ѹ�������֮��Ӧ��һ�����ʵ�ȥ������Լ�С�����������ڲ����ʱ�ùܽſս� |

| AGND | 12,64 | �ڲ�����ض� |

| GLMA | 10,66 | ��Ԫȫ�ֹܽţ����ô˹ܽ���Ϊ�ڲ������Ҫ�ⲿ����ʱ�����룬����Ҳ������Ϊ��ͨI/Oʹ�� |

| GND | 1,9,25,38,40,51,67,75,86,88 | �ӵ� |