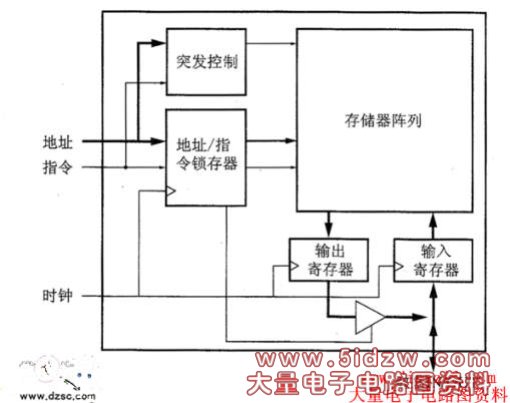

同步管道突发式SRAM大体的结构如图所示。这种类型的SRAM需要考虑适应CPU的突发传输模式,图中“突发控制”部分就是为此设计的电路。

现在的CPU都在内部装载高速缓冲存储器,以便于提高对连续区域的存取效率。即使针对外部总线,也设计了类似提高对连续区域存取效率的总线周期,该总线周期称为突发传输周期。

在突发传输周期中,虽然通常是将连续4字的数据汇总后进行传输,但只要知道开始地址,之后就可确定存取地址的顺序。因此,像通常存储器的存取方式那样,不必输出每次的地址,只要输出最初的地址,之后与时钟同步,就可连续输出数据,这样就可以实现高速化的目标。

对此,在同步SRAM上,对应于该突发传输周期,只要给予最初的地址,就可以实现通过自身自动生成下一个地址,然后进行数据的读/写操作。之所以称为“同步突发”及“同步管道突发”,是为了表示这是对应于突发传输操作的。

在个人计算机的世界中,同步管道突发式SRAM在奔腾(Pentium)类处理器成为主流之前经常作为二级高速缓冲存储器使用。近期的CPU为了提高性能都内置了二级高速缓冲存储器。在外部即使附加高速缓冲存储器作为三级缓存,其性能也未提高多少。因此,在个人计算机的母板上已经很少能看到同步管道突发式SRAM。

欢迎转载,信息,同步管道突发式SRAM