标签:fpga是什么,fpga教程,fpga培训,http://www.5idzw.com

用XC9572实现HDB3编解码设计,http://www.5idzw.com

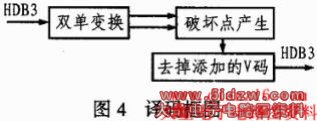

HDB3编解码的CPLD设计可采用上面介绍的FOUNDATION ISE 4.2I 开发工具来实现。设计输入采用Verilog HDL语言完成。设计分为三个模块:时钟模块、编码模块、译码模块。限于篇幅,本文未给出时钟模块、编码模块及译码模块的源代码。有需要者,可和作者联系。

5 结束语

本文介绍的用CPLD 实现HDB3编解码电路具有电路简单、可靠、价格便宜等优点。将该电路用于10MHz以太网到E1信号相互转接通信设备中后,经过实际测试,其性能指标完全能够满足CCITT建议G.703标准。另外,通过修改时钟提取部分及更换晶体,该电路还可用于其它速率的HDB3编解码

,用XC9572实现HDB3编解码设计