矩阵向量乘法器仿真结果验证

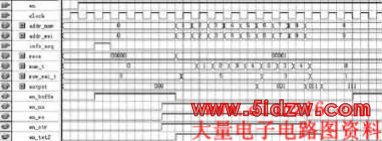

在Quartus II环境下,实现output=Xs,得到如图5所示时序图。

图5 output="Xs仿真时序图"

图5中“en”是使能信号,“clock”是时钟信号,addr_num、addr_wei分别为两个存储器的地址信号,info_seq是输入信息信号,rece是信息信号经过缓存后的输出信号,num_t是“1”在各行的位置信息,row_wei_t是相应各行的行重,output是矩阵与向量相乘的结果。由图5可知,output=[1 1 1],信号输出有一个时钟周期的延时,仿真结果正确。

编码器方案验证与优缺点分析

本文利用FPGA实现了基于RU算法的编码器设计实现。在Quartus II软件环境下对LDPC编码器进行仿真,使用Stratix系列EP1s25F672I7芯片,对码长为504的码字进行编码。编码器占用约9%的逻辑单元,约5%的存储单元,综合后时钟频率达到120MHz,数据吞吐率达到33Mb/s,基本符合编码器设计的要求。该编码器结构是一种通用的设计方案,可以应用于各种不同的LDPC编码中,但由于其采用通用的编码算法,实现的复杂度高于某些特殊结构的LDPC码编码器,比如准循环LDPC码。另外通过优化时序和编码结构,可以进一步提高本文的编码器的编码速度。

,利用FPGA实现基于RU算法编码器(LDPC编码器)的设计