RGB数据输出顺序反转:配合Common电压反转,控制液晶面板根据电平值,显示正确的色彩如图4所示。

图4 Common电压与RGB时序

锁相环电路:在PLL时钟模式下,外部的VCO振荡电路在某些不稳定因素影响下,其输出时钟频率会产生漂移,直接影响TCON模块的正常工作,间接影响了整个TFT-LCD系统。为了防止这种情况发生,TCON模块会产生一个时钟的相位比较信号,通过锁相环电路,使VCO输出的工作时钟频率稳定在一个允许范围之内。

3.4 时序控制模块的结构

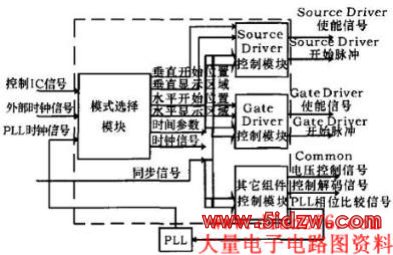

根据上述分析,给出时序控制模块的一种结构框图,如图5所示:

图5 时序控制模块结构框图

模式选择模块用来确定LCD分辨率及工作模式,选择合适时钟信号,产生所需的时间参数(如输出控制信号脉宽等),以及水平、垂直开始位置及显示区域信息,用于控制Driver正确显示有效数据。Source Driver控制模块根据模式选择所产生的时间参数和垂直开始位置及显示区域,对每场的开始行位置及每场显示行数进行限制,再配合行、场同步信号时序,输出控制信号使Source Driver正常工作。对于不同分辨率的显示屏,Source Driver的采样周期不同,分辨率越高,每个像素采样时间就会越短,以便在固定的场、行周期内显示完整画面。类似地,Gate Driver控制模块则是根据模式选择所产生的时间参数和水平开始位置及显示区域,对每行的开始点及每行显示区域进行限制,再配合

行、场同步信号时序,输出控制信号使Gate Driver正常工作。

其它组件控制模块在Driver工作时,由行、场同步信号及时间参数,控制其它一些组件与Driver工作时序相匹配,使LCD面板正常显示。

4 FPGA逻辑功能验证

参照图5中的结构图,用Verilog语言对时序控制模块进行行为级描述,并结合TFT-LCD其它组件,进行FPGA逻辑功能验证。

本文选用XILINX 公司Spartan-II系列XC2S200芯片作为目标芯片,该芯片集成有20万个等效逻辑门,含有5,292个逻辑单元,最高工作频率可以达到200MHz以上。以Modelsim5.5为仿真平台,运用Verilog HDL语言描述了整个结构,并进行了编译、仿真及下载验证。仿真环境:输

入时钟源为PLL模式,TFT-LCD分辨率为480×234,NTSC制式,复合同步模式。

只有在相应工作模式所要求的显示区域内Driver的控制信号才有有效输出,与其它控制信号时序相匹配。TFT-LCD显示正常。

5 结束语

TFT-LCD显示系统工作时各模块的协同配合至关重要。TCON模块结构的设计直接影响了其输出显示时序信号的正确性与工作效率,作为

TFT-LCD显示系统的中心控制模块,它负责控制LCD系统中最重点的显示部分,是使其达到良好的显示效果的关键。本文以Modelsim5.5为仿真平台,运用VerilogHDL语言描述了整个结构,并进行了编译、仿真,选用XILINX公司Spartan-II系列XC2S200芯片作为目标芯片进行验证,给出仿真与验证结果。实践证明,LCD显示效果良好,本文提出的TCON模块设计是可行的,可以参考。