3 各种HDL语言的体系结构和设计方法

3.1 SystemC

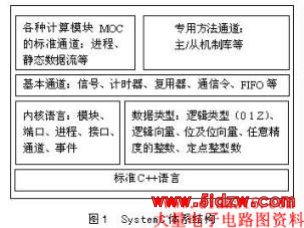

所有的SystemC都是基于C++的;图1中的上层构架都是很明确地建立在下层的基础上;SystemC内核提供一个用于系统体系结构、并行、通信和同步时钟描述的模块;完全支持内核描绘以外的数据类型、用户定义数据类型;通常的通信方式,如信号、FIFO,都可以在内核的基础上建立,经常使用的计算模块也可以在内核基础上建立;如果需要,图1中较低层的内容不依赖上层就可以直接使用。

实际使用中,SystemC由一组描述类库和一个包含仿真核的库组成。在用户的描述程序中,必须包括相应的类库,可以通过通常的ANSI C++编译器编译该程序。SystemC提供了软件、硬件和系统模块。用户可以在不同的层次上自由选择,建立自己的系统模型,进行仿真、优化、验证、综合等等。

3.2 Superlog

Superlog集合了Verilog的简洁、C语言的强大、功能验证和系统级结构设计等特征,是一种高速的硬件描述语言。其体系结构如图2。

① Verilog 95和Verilog 2K。Superlog是Verilog HDL的超集,支持最新的Verilog 2K的硬件模型。

② C和C++语言。Superlog提供C语言的结构、类型、指针,同时具有C++面对对象的特性。

③ Superlog扩展综合子集ESS。ESS提供一种新的硬件描述的综合抽象级。

④ 强大的验证功能。自动测试基准,如随机数据产生、功能覆盖、各种专有检查等。 Superlog的系统级硬件开发工具主要有Co- Design Automation公司的SYSTEMSIMTM和SYSTEMEXTM,同时可以结合其它的EDA工具进行开发。

3.3 Verilog和VHDL

这两种语言是传统硬件描述语言,有很多的书籍和资料可以查阅参考,这里不多介绍。

4 目前可取可行的策略和方式

按传统方法,我们将硬件抽象级的模型类型分为以下五种:

◇ 系统级(system)――用语言提供的高级结构实现算法运行的模型;

◇ 算法级(algorithm)――用语言提供的高级结构实现算法运行的模型;

◇ RTL级(Register Transfer Level)――描述数据在寄存器之间流动和如何处理、控制这些数据流动的模型。(以上三种都属于行为描述,只有RTL级才与逻辑电路有明确的对应关系。)

◇ 门级(gate-level)――描述逻辑门以及逻辑门之间的连接模型。(与逻辑电路有确切的连接关系。以上四种,数字系统设计工程师必须掌握。)

◇ 开关级(switch-level)――描述器件中三极管和存储节点以及它们之间连接的模型。(与具体的物理电路有对应关系,工艺库元件和宏部件设计人员必须掌握。)

根据目前芯片设计的发展趋势,验证级和综合抽象级也有可能成为一种标准级别。因为它们适合于IP核复用和系统级仿真综合优化的需要,而软件(嵌入式、固件式)也越来越成为一个和系统密切相关的抽象级别。

目前,对于一个系统芯片设计项目,可以采用的方案包括以下几种:

① 最传统的办法是,在系统级采用VHDL,在软件级采用C语言,在实现级采用Verilog。目前,VHDL与Verilog的互操作性已经逐步走向标准化,但软件与硬件的协调设计还是一个很具挑战性的工作,因为软件越来越成为SOC设计的关键。该方案的特点是:风险小,集成难度大,与原有方法完全兼容,有现成的开发工具;但工具集成由开发者自行负责完成。

② 系统级及软件级采用Superlog,硬件级和实现级均采用Verilog HDL描述,这样和原有的硬件设计可以兼容。只要重新采购两个Superlog开发工具SYSTEMSIMTM和SYSTEMEXTM即可。该方案特点是风险较小,易于集成,与原硬件设计兼容性好,有集成开发环境。

③ 系统级和软件级采用SystemC,硬件级采用SystemC与常规的Verilog HDL互相转换,与原来的软件编译环境完全兼容。开发者只需要一组描述类库和一个包含仿真核的库,就可以在通常的ANSI C++编译器环境下开发;但硬件描述与原有方法完全不兼容。该方案特点是风险较大,与原软件开发兼容性好,硬件开发有风险。 5 未来发展和技术方向

微电子设计工业的设计线宽已经从0.25μm向 0.18μm变迁,而且正在向0.13μm和90nm的目标努力迈进。到0.13μm这个目标后,90%的信号延迟将由线路互连所产生。为了设计工作频率近2GHz的高性能电路,就必须解决感应、电迁移和衬底噪声问题(同时还有设计复杂度问题)。

未来几年的设计中所面临的挑战有哪些?标准组织怎样去面对?当设计线宽降到0.13μm,甚至更小时,将会出现四个主要的趋势:

◇ 设计再利用;

◇ 设计验证(包括硬件和软件);

◇ 互连问题将决定对时间、电源及噪声要求;

◇ 系统级芯片设计要求。

满足未来设计者需要的设计环境将是多家供应商提供解决方案的模式,因为涉及的问题面太广且太复杂,没有哪个公司或实体可以独立解决。实际上,人们完全有理由认为,对下一代设计问题解决方案的贡献,基础研究活动与独立产业的作用将同等重要。

以后,EDA界将在以下三个方面开展工作。

① 互用性标准。所有解决方案的基础,是设计工具开发过程的组件――互用性标准。我们知道,EDA工业采用的是工业上所需要的标准,而不管标准是谁制定的。但是,当今市场的迅速发展正在将优势转向那些提供标准时能做到快速适应和技术领先的组织。处于领先的公司正在有目的地向这方面投资,那些没有参加开发这些标准的公司则必须独自承担风险。 ② 扩展其高级库格式(ALF)标准,使其包含物理领域的信息,是EDA开发商可以致力于解决互连问题的算法,从而使电路设计者在解决设计收尾工作时,不再受到这个问题的困扰。

③ 制定新的系统级设计语言标准。标准化系统芯片的设计工具和语言,使SoC真正达到第三次微电子设计革命浪潮。

5 国内发展的战略选择

由于目前IT行业不景气,以及ASIC设计复杂程度不断增加,各EDA公司出现了合并调整的趋势。Synopsys合了Avant!和Co-Design,Cadence合了GDA等,形成了几大巨头的局面。而各可编程器件厂商,像Xilinx和Altera,也积极与EDA紧密合作,因此,我们必须抓住这个时机,全力发展;不然,就要面对以后与垄断巨头进行竞争的事倍功半的不利局面。

针对目前硬件描述语言的发展和国家芯片制造生产的发展战略,国内如何在原EDA基础薄弱的情况下迅速发展,使EDA成为一个合理、健康而必不可少的产业;将基础研究活动与独立产业的作用合理的结合,建议开展如下方面的工作:

① 为了实现我国的芯片设计自主化,必须夯实基础,在结合VHDL的基础上,推广Verilog HDL设计语言,使硬件设计的底层单元库可以自主研制;

② 根据目前芯片系统的发展趋势,对系统级语言进行比较研究,在Suoerlog、SystemC等语言中做出选择,并进行相关工具的推广,以及与相关企业进行合作等;

③ 深入HDL语言的综合和仿真等模型的研究,努力在与国外合作的基础上,建立自主知识产权的EDA公司;

④ 积极加入EDA目前正在进行的标准化工作,做到了解、学习、应用、吸收、参与并重;

⑤ 政府积极加入,重视产、学、研的合作,开展卓有成效的发展模式。