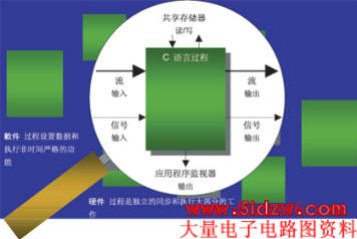

图1,在应用调试和监视过程中连接硬件和软件过程

设计实例:基于FPGA的图像虑波器

为了演示这些工具如何用来把算法过程移至FPGA,我们以图像虑波器为例,其中输入数据流必须非常快速地处理,生成输出数据流。这样的问题可能涉及大量的计算,而且也是对带宽要求非常高。

图2说明一个简单的图像虑波器如何工作。在所示的示例中(边缘检测虑波器),尤其是3×3窗口的像素数据必须以流方式组合和处理。

图2,图像虑波器过程一次处理输入图像一个像素,在最近的八个像素进行卷积

有许多可能的方法实现这种算法。在本例中,两个流水式硬件处理器用C描述完成这种功能:一个过程生成匹配源图像的匹配行像素(以像素流读取),同时第二个过程接受第一个过程的数据流的结果,将对每个像素窗口卷积,生成一个输出图像,用第二个过程中单一的卷积像素流表示。这个过程和流用Impulse C库(见附文《Impluse C编程模型》)提供的C兼容的流I/O例程来声明和读/写。

因为算法是用标准C(外加Impulse C库)描述的,我们能从软件设计(用Microsoft Visual Studio开发)开始,它在桌面仿真环境下完成图像算法。这种设计将两种硬件过程和图像卷积功能结合到软件台设计中(它可以编译,并以基于PC的台式机应用或运行在Nios处理器中的嵌入式应用运行),它从TIFF格式文件中读取数据进行处理。这种设计可以用标准桌面调试工具和CoDeveloper Application Monitor进行设置和运行。在这种方式下,算法结果可以在编译到FPGA平台之前进行验证。

编译为硬件

用标准桌面C开发工具仿真它的功能之后,我们准备用Altera Stratix开发原型板,在混合FPGA/处理器目标上实现该应用。Altera Nios开发包包括所有编译和综合至FPGA所需的硬件和软件(包括自动生成的硬件过程的HDL源文件和表示软件过程的C源代码)。Altera提供的软件结合Impulse CoDeveloper,为我们提供了从C语言编译和执行测试应用所需的一切。

我们第一步是为图像滤波器本身生成硬件。为了达到这一目的,我们从CoDeveloper工具中选用Altera Nios Platform Support Package,处理相关的Impulse C源文件。这将产生大约1200行的RTL和相关的硬件/软件接口源文件。

接下来,用Altera Quartus工具建立新的项目,生成包括必要外设的Nios处理器核(用Altera的SOPC Builder)。CoDeveloper输出生成的硬件和软件文件给Quartus。使用Altera的框图工具,我们通过Avalon片内总线将生成的硬件过程和Nios处理器相连。

整个系统用Altera Quartus综合。应用的软件部分(主要由测试生成器和客户功能组成,包括组函数)也导入Quartus项目,用所包含的Nios编译器编译。

最后,用Altera工具生成bit文件,通过提供的并口电缆下载到平台上。在这个平台按预期要求上电和运行。

在这个例子中,显式流水的两个图像滤波器过程和由CoDeveloper C自动为硬件编译器生成的流水在每两个FPGA时钟周期获得最佳的单像素图像处理速率,相当于大约10ms完成整个512×512图像的处理速度。

当然,在FPGA上任何算法的性能是取决于I/O因素及算法本身。在我们的图像滤波器测试方案中,图像数据从Nios上运行的测试生成器通过Avalon片内互连传送到生成的FPGA硬件上,这样可以获得比上述最大像素速率低得多的有效吞吐量。另一个算法版本中,像素数据直接从FPGA硬件接口传送和读取,这样做的结果会最接近最佳的结果。因此考虑带宽的限制是非常重要的。象CoDeveloper这样的工具可以更容易和更快地进行这方面的评估和实验。

附文:Impluse C编程模型

建立软件和硬件相结合的设计需要对并行编程技术有所了解。为了帮助建立高度并行的混合硬件/软件应用,Impulse C库包括了设置和管理多个独立过程的功能,它可以通过数据流、信号和可选的共享存储资源相连接。

Impulse C编程模型(概念上和1980年C.A.R.Hoare描述的通信时序处理模型类似)提供了对硬件/软件划分和同步的系统级控制,同时允许用标准C构造编写和自动优化独立过程。

图a,Impulse C编程模型:通信主要通过数据流(映射为生成硬件中的FIFO),其它需要同步的信号,本地存储器。

使用Impulse C库功能,C语言可用来描述高度并行的应用,具有最小的软件编程复杂度,同时具有用标准C开发环境下编译和调试的能力。例如,使用Impulse C库功能,一个简单的图像滤波器可以用如下的代码风格描述(实际算法省略)

这设计方法的结果是底层硬件平台的实际情况被抽象,用户(他可能是有经验的C程序员,但几乎没有硬件设计知识)不必学习硬件设计方法,就可以描述和运行混合软件/硬件应用。