同时,还可以利用QuartusII的SigTapII工具对所设计的程序进行硬件验证,设置好相应步进后,相应的输出波形如图5及图6所示。可见所产生的低频正弦信号波形平滑,而频率较高时有一定的毛刺,这可以通过后级的低通滤波电路(如切比雪夫低通滤波网络等)来进行滤除。

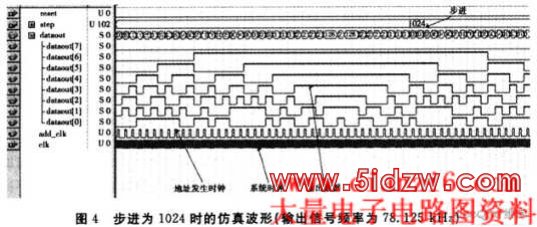

本设计使用的逻辑单元只占FPGA片上资源的1%,存储单元占54%,I/O口占13%。可见主要资源为片上的存储单元,如果提高一位地址位,则数据量翻倍,FPGA片上ROM不够用。通过QuartusII6.0的时钟分析,本设计可达到的最高时钟为149.41 MHz,而地址发生的时钟为时钟的4分频,故地址发生单元的最高时钟可达37.352 5 MHz,相应的输出信号最高频率可达4.665 MHz,相应的最低频率及频率步进为284.976 Hz。

5 结束语

本设计在不向外扩展ROM存储器的情况下,对DDFS设计进行优化,充分利用Cyclone II系列FPGA的片上资源,其输出正弦信号最高频率可达4 MHz以上。只要采用更好的方案进行设计,使采样点可以做到232个及以上,频率分辨率可以做到0.015 Hz,达到mHz量级,进一步提高信号源的输出信号频率范围及频率分辨率等技术指标,可利用Cyclone II系列芯片设计出性能优良的信号源,达到实用信号源的要求。

,基于CycloneII系列FPGA的DDFS信号源实现