内置闪存的FPGA

非易失FPGA提供额外的Flash保护安全功能,可以防止内存因意外或未经授权的操作被擦除或重新编程。Flash保护功能采用64位密钥。

对器件进行删除或重新编程时, ispVM System会核查Flash是否被保护。如果是,就要求用户输入64位密钥,然后ispVM检查这个密钥是否与存储在器件中的密钥一致,如果一致就执行操作。但是,如果丢失了密钥,器件就再也不能被擦除了。

这些安全性措施不仅保护了用户电路板上的设计,而且也防止了试图修改系统功能的盗版行为。这些功能还有助于远程的系统更新。莱迪思FPGA提供这一功能,使用户可以通过对FPGA重复编程来更新他们的系统,而不会中断它与周围元件的联系。此功能被称为TransFR 。

FPGA最值得注意的的特点是设计人员很容易对器件进行重构。但是,重构通常意味着系统要中断很长时间。但是,莱迪思开发的TransFR技术将重构的影响降至最低。莱迪思的几个FPGA系列都支持TransFR技术,包括那些含有内置闪存的器件,如MachXO 、LatticeXP和LatticeXP2 ,以及像LatticeECP2 /M那样的SRAM FPGA。

图5 用最短的中断系统时间进行远程更新

TransFR是一种同时使用基本任务编程和边界扫描单元的技术。基本任务编程修改非易失存储器的内容(内部的或外部的) ,以便使FPGA的SRAM部分继续工作。莱迪思的FPGA拥有可以取样和预加载的边界扫描单元,可以在编程时控制FPGA的I/O。

图6 执行TransFR的4个步骤

执行TransFR的4个步骤:

1,进行基本任务编程。系统对FPGA的非易失性存储器再编程,但不会中断SRAM的功能。

2,可以锁定I/O的状态,用户可以保持或预先确定I/O的状态。在整个重新配置过程中,I/O的值保持不变,以防止系统被关闭。

3, 接着用JTAG命令把新的配置传输至非易失存储器。一完成对SRAM就执行全局复位,以便使该器件处于一个已知的状态。然后释放I/O的状态,并再次锁定PLL。

4,释放输出,内部逻辑停止对I/O的监测。

要使用TransFR,需要用到ispLEVER开发工具和ispVM。

用户通过使用128位AES密钥加密文件和Lattice TransFR技术完成了更新过程,但仍有可能因为系统本身的弱点或违法行为引发系统故障。虽然FPGA的位流是加密的,但是非法操作或传输中的错误都可能损坏它,从而导致FPGA被阻塞,使系统无法正确地重启。为了解决这个问题,莱迪思推出了“双引导 ”功能。

双引导配置

在配置存储器中存储两个编程文件。

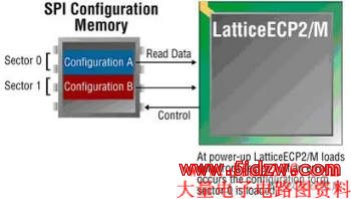

图7 双引导配置

激活PROGRAM引脚或启动JTAG刷新指令后,FPGA下载存储在Sector 1的位流 。如果CRC出错,FPGA自动恢复到Sector 0配置。Lattice XP2非易失FPGA也有此功能。该Flash元件拥有主动配置,还有一个用来存放安全( “golden” )配置的SPI Flash。

莱迪思拥有许多能帮助设计人员保障设计安全的产品。Lattice ECP2/M FPGA是一款拥有128位AES密钥的高安全性器件。这些经济的器件提供了大存储容量(高达5.3 Mbit)、高速I/O和SERDES 。非易失性LatticeXP2 FPGA是市场上一款很独特的器件,它有着极高的安全性。由于采用了FlexiFlash技术,位流存储在器件的Flash中, 并由128位AES密钥对它进行保护。此外, TransFR更是保障了绝对安全的远程系统更新。

设计的安全性应该是设计过程的一部分,而不是事后再去考虑。无论选择了哪种技术,最重要的是要防止设计被篡改,无论这个篡改行为是无意的还是非法的。

,FPGA设计的安全性